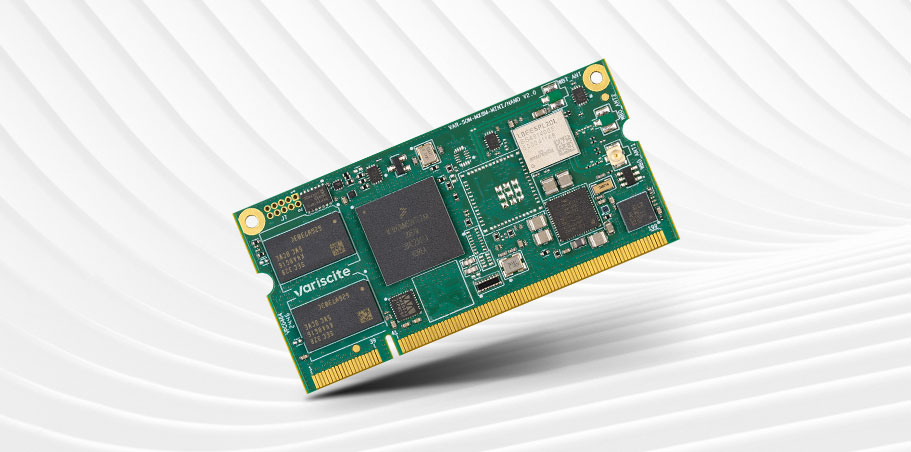

Highlights

CPU

Up to 6x 2.0GHz Arm Cortex-A55 + 800MHz Arm Cortex-M7 + 250MHz Arm Cortex-M33

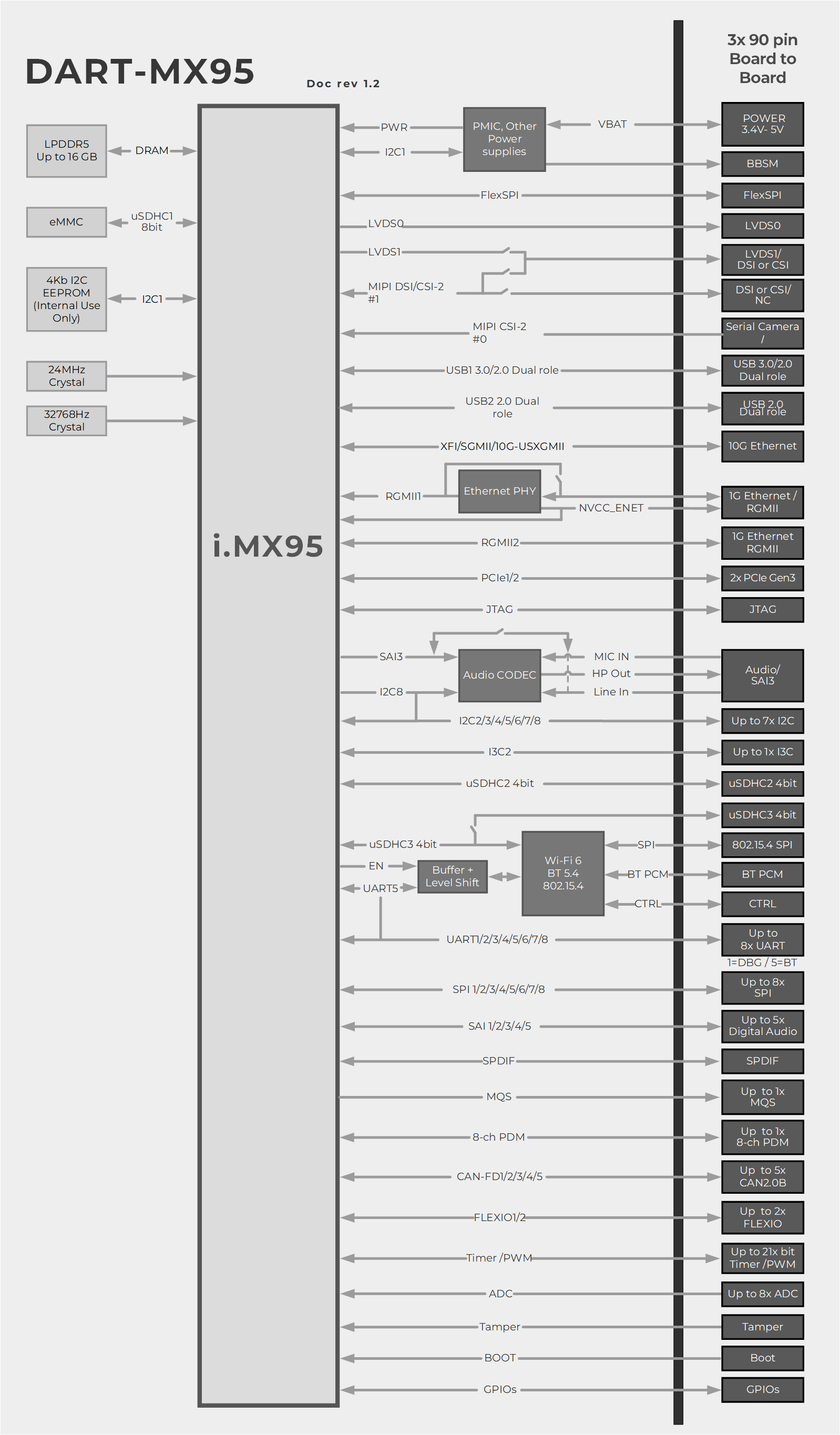

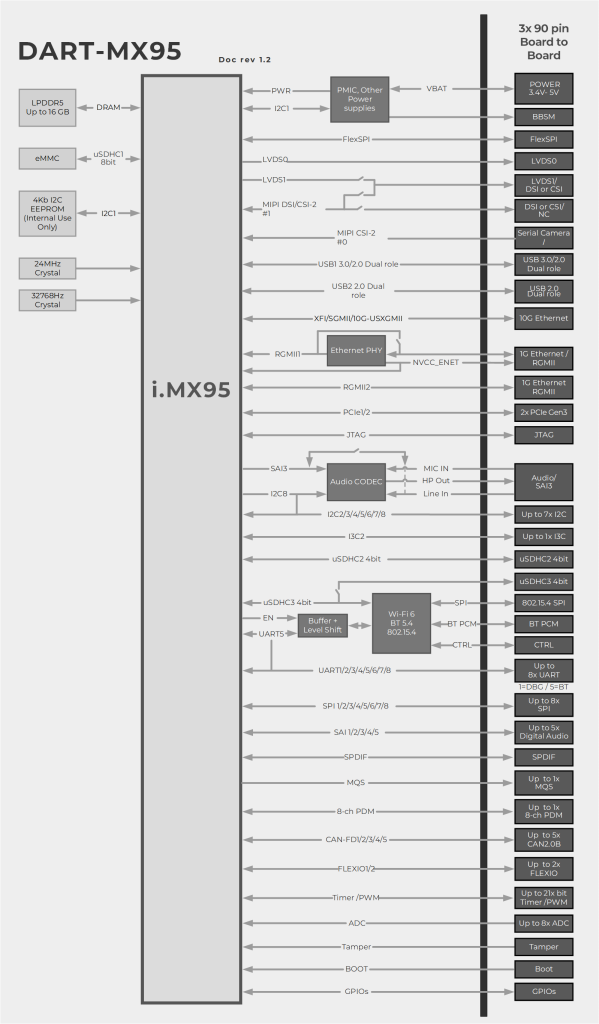

High Speed Interfaces

1x USB3.0/2.0 + 1x USB2.0, 2x GbE + 10GbE, 2x PCIe

Certified WiFi/BT

Wi-Fi 6 802.11 ax/ac/a/b/g/n with optional 802.15.4 and BT/BLE 5.4

Temperature range

-40 to 85°C

Multimedia

AI/ML acceleration, 2D/3D GPU, 4K UltraHD decode/encode and display

Product Longevity

2039

Assistenza

Siamo con te passo passo, dal concept del prodotto al lancio... e oltre.

Assistenza gratuita e immediata direttamente dagli esperti R&D Variscite.

Collegamenti rapidi

Specifiche

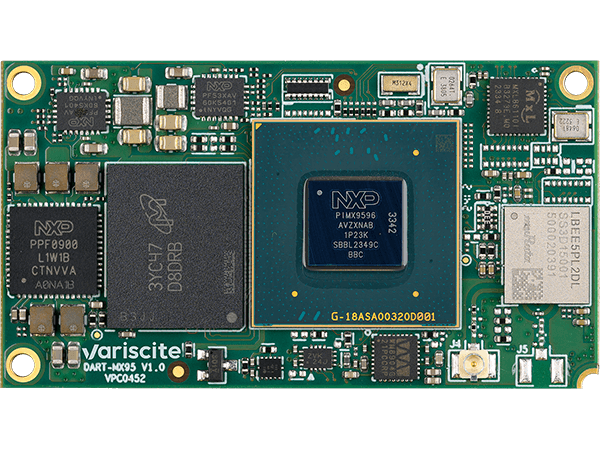

CPU Name

NXP i.MX 95

CPU Type

Cortex™-A55

CPU Cores

4-6 cores

CPU Clock (Max)

Up to 2.0GHz

Real-time co-processor

800 MHz Cortex-M7

333Mhz Cortex-M33

333Mhz Cortex-M33

RAM

2 – 16GB LPDDR5

eMMC

8 – 128 GB

Multimedia

2D/3D Graphics Acceleration

3D GPU with OpenGL® ES 3.2, Vulkan® 1.2, OpenCL™ 3.0

2D GPU

2D GPU

Video Encode / Decode

4Kp30 H.265 and H.264 encode and decode

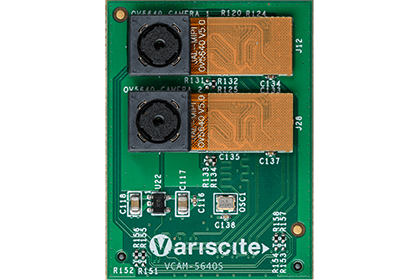

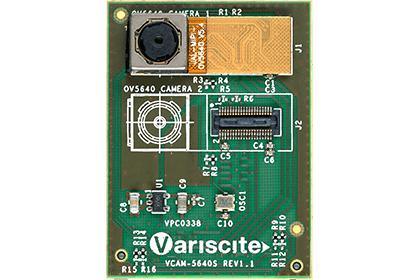

Camera Interfaces

2x MIPI CSI2

AI/ML

AI/ML NPU acceleration 2 TOPS

Image Signal Processor (ISP)

Yes

Display

DSI

MIPI-DSI 4kp30 or 3840x1440p60

LVDS

Dual 1920x1080 24-bit

Touch controller

Resistive, Capacitive

Audio

Headphone driver

Yes

Microphone

Digital, Analog (stereo)

Digital audio serial interface

5 x I2S(SAI),S/PDIF,RX TX, PDM 8CH, MQS

Line In/Out

Yes

Connectivity

SD / MMC

x1

USB Host / Device

USB 3.0/2.0 1x OTG; USB 2.0 1x Dual role

UART

x8

I2C

x7

I3C

X1

SPI

x8

CAN Bus

x5

RTC

On carrier

JTAG

X1

QSPI

X1

PCI-Express

X2 Gen 3.0

ADC

x8

Networking

Ethernet

2x 10/100/1000 Mbps (2x Ethernet with TSN support)

1x 10 Gbps (Ethernet with TSN support)

1x 10 Gbps (Ethernet with TSN support)

Wi-Fi

Certified Wi-Fi 6 dual-band 802.11ax/ac/a/b/g/n with optional 802.15.4, matter

Bluetooth

BT/BLE5.4

Linux

Yocto, Debian

Android

Yes

FreeRTOS

Yes

Zephyr

Yes

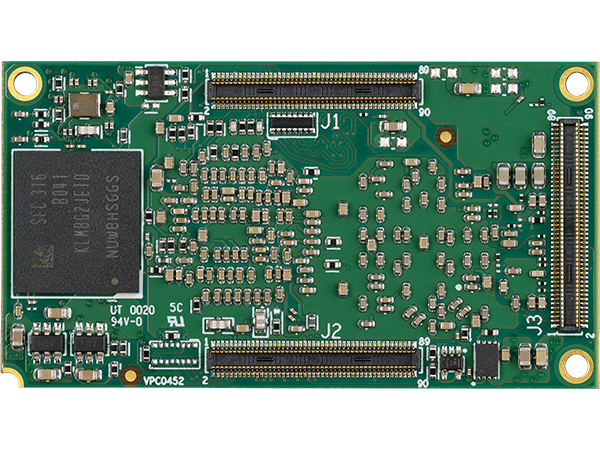

Mechanical Specifications

Dimensions (W x L)

55.0 x 30.0 mm

Electronic Specifications

Supply voltage

3.4V- 5V

Digital I/O voltage

3.3V/1.8V

Environmental Specifications

Commercial operating temperature

0 to 70°C

Extended operating temperature

-25 to 85°C

Industrial operating temperature

-40 to 85°C

Storage temperature

-40 to 85°C

Storage humidity

5% to 95%

DART-MX95[x]_[xxxx]C_[xx]R_[xx]G_[AC]_[EC]_[WBD/WBE]_[DSCM]_[ADC]_[CMP]_[SDEX]_[X]T

MX95[x]

CPU type:

6 Cores: H

4 Cores: Q

6 Cores: H

4 Cores: Q

[xxxx]C

CPU clock speed: 2000MHz: 2000C, 1800MHz: 1800C

[xx]R

LP-DDR5: 2GB: 2R, 4GB: 4R, 8GB: 8R, 16GB: 16R

[xx]G

eMMC: 8GB: 8G, 16GB: 16G, 32GB: 32G, 64GB: 64G, 128GB: 128G

[AC]:

Audio Codec

[EC]:

GbE PHY on first ethernet port

[WBD/WBE]

WBD:

Built-in certified dual band Wi-Fi 802.11 ax/ac/a/b/g/n + BT/BLE 5.4

WBE:

Built-in certified dual band Wi-Fi 802.11 ax/ac/a/b/g/n + BT/BLE 5.4 + 802.15.4

Built-in certified dual band Wi-Fi 802.11 ax/ac/a/b/g/n + BT/BLE 5.4

WBE:

Built-in certified dual band Wi-Fi 802.11 ax/ac/a/b/g/n + BT/BLE 5.4 + 802.15.4

[DSCM]

Default: Dual LVDS (#0 and #1) plus DSI

DSCM: LVDS #0, DSI in pin2pin compatible mode instead of LVDS #1

DSCM: LVDS #0, DSI in pin2pin compatible mode instead of LVDS #1

[ADC]

Export ADC lines

[CMP]

Instead of power pins, J3.15/27/34/63 are not connected for compatibility with other DART SoMs

[SDEX]

Default: no extra SDIO

SDEX: extra SDIO port, available only when no WBD/WBE is selected

SDEX: extra SDIO port, available only when no WBD/WBE is selected

[x]T:

C : 0 to 70°C, E: -25 to 85°C, I : -40 to 85°C

Note: All options in [brackets] are optional add-ons that can be either removed or selected from a list of options

Le nostre partnership di lunga data

I nostri stretti rapporti con i principali fornitori di tecnologia offrono ai nostri clienti un accesso in anteprima alle ultime soluzioni avanzate: i tuoi progetti partiranno da una base solida anche in prospettiva futura.

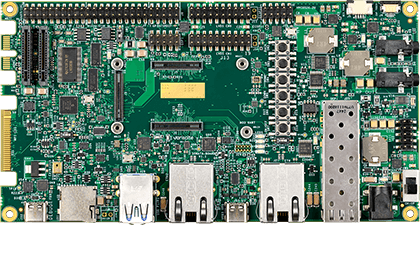

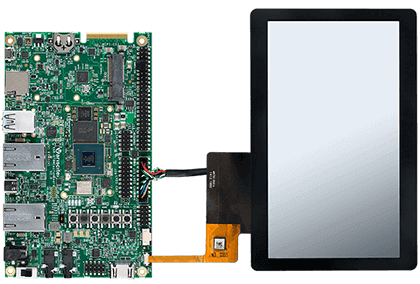

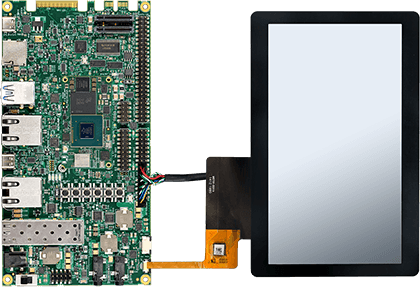

Evaluation Kit

DART-MX95 Evaluation Kits

Chiedi un preventivo personalizzato

Compila i campi di seguito e un nostro rappresentante ti contatterà a breve

Why Variscite?

Qualità

Produzione in-house con controllo di qualità completo - certificato secondo gli standard medici ISO 9001 e ISO 13485.

Pin2Pin

Le nostre famiglie di prodotti Pin2Pin garantiscono la massima scalabilità e di poter passare senza problemi a tecnologie future senza riprogettare la scheda portante.

Longevità

Disponibilità hardware garantita per 15 anni e supportata da aggiornamenti software e assistenza continui.

Personalizzazione

Configura il tuo sistema con precisione e flessibilità: scegli solo le funzioni necessarie e taglia i costi.

Aggiornamenti

Rimani aggiornato con gli aggiornamenti software: mantieni i tuoi SoM Variscite sempre al massimo delle loro prestazioni con le nostre ultime versioni software.

23.02.2026

Variscite, leader mondiale nella progettazione e produzione di System on Module, presenta la nuova serie di moduli conformi allo standard Smart Mobility Architecture (SMARC). Il VAR-SMARC-MX8M-PLUS segna il debutto di questo portafoglio alimentato da processore NXP i.MX 8M Plus.

29.01.2026

La scelta del partner SoM parte dalla comprensione dei modelli di produzione

27.11.2025